第三届国际先进光刻技术研讨会在南京开幕

10月17日,第三届国际先进光刻技术研讨会在南京开幕,会议由集成电路产业技术创新联盟和中国光学学会主办,中国科学院微电子研究所、南京市浦口高新区和南京市浦口区科学技术局承办,南京诚芯集成电路技术研究院协办,IEEE南京分会提供技术支持。本次会议由中芯国际(SMIC)、长江存储(YMTC)、华虹集团、Mentor、Photronics、KLA、ASML、TEL、ZEISS、JSR、Synopsys、上海微电子装备(集团)股份有限公司(SMEE)、ASML Brion、积塔半导体、Cymer、南大光电(Nata)、沈阳芯源等国内外企业提供赞助。来自中国、美国、德国、日本等世界各地众多名企、厂商、科研机构、高校的共计400余名技术专家和学者参加了本届大会。

会议开始,大会主席、集成电路产业技术创新联盟理事长、科技部原副部长曹健林研究员,国家科技重大专项电子信息领域监督评估组组长、国家外国专家局原局长马俊如研究员,大会副主席、中国科学院微电子研究所所长、国家02科技重大专项技术总师叶甜春研究员,南京市浦口区区委副书记、区长曹海连,中国光学学会秘书长、浙江大学光电工程研究所所长刘旭教授,以及IEEE 终身会士、ALITECS公司资深经理Shinji Okazaki分别致辞。大会秘书长、中科院微电子研究所计算光刻研发中心主任韦亚一研究员主持开幕式。

按照大会安排,在这两天的时间里,来自Intel、IBM、Mentor等公司的专家作特邀报告,深入分析光刻领域先进节点最新的技术手段和解决方案,内容丰富,包含先进节点的计算光刻技术、SMO、DTCO、EUV、DSA、Deep Learning、设备、材料等。

据悉,作为国内首个国际高端光刻技术研讨会,已连续举办两届,本届大会延续了往届的高规格和高水准,已成为共享国内外先进光刻技术研发成果,促进我国集成电路制造技术研发与应用,开展合作与交流的高端峰会。

以下是会议详细内容:

▲大会主席、集成电路产业技术创新联盟理事长、科技部原副部长曹健林研究员致开幕词

▲国家科技重大专项电子信息领域监督评估组组长、国家外国专家局原局长马俊如研究员致开幕词

▲大会副主席、中国科学院微电子研究所所长、国家02科技重大专项技术总师叶甜春研究员致开幕词

▲南京市浦口区区委副书记、区长曹海连致开幕词

▲中国光学学会秘书长、浙江大学光电工程研究所所长刘旭教授致开幕词

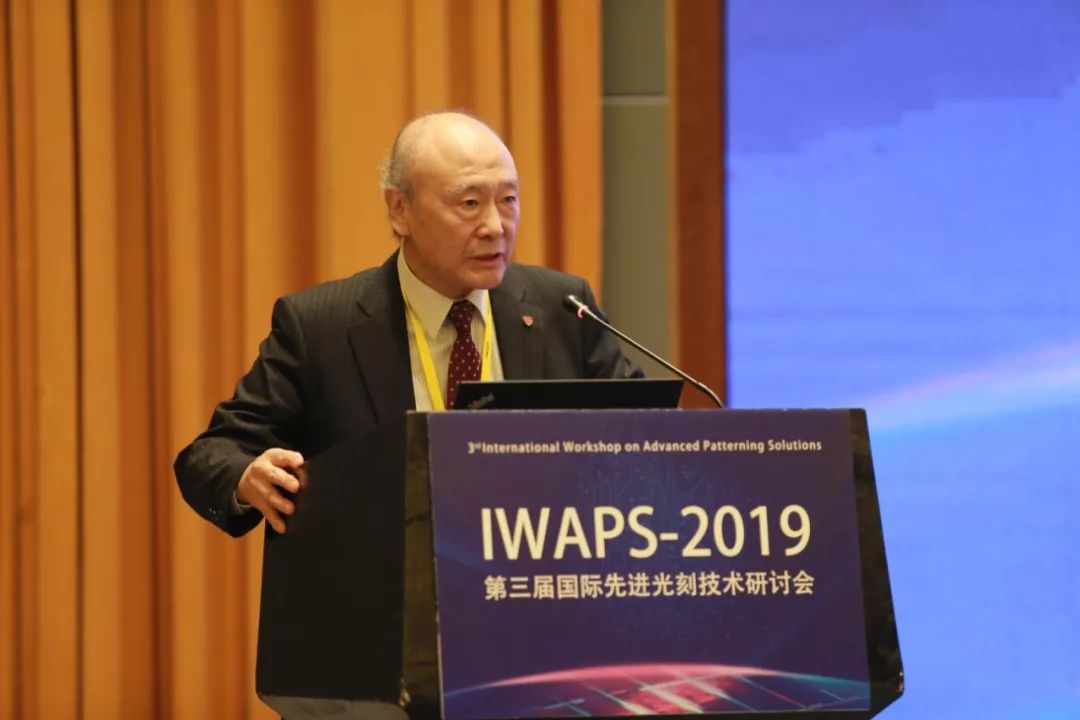

▲IEEE 终身会士、ALITECS公司资深经理Shinji Okazaki致开幕词

▲大会秘书长、中科院微电子研究所计算光刻研发中心主任韦亚一研究员主持开幕式

以下是会议报告内容:

来自Lawrence BerkeleyNational Lab的PatrickNaulleau的报告介绍了极紫外(EUV)光刻现在在7纳米节点及其以后的大规模生产中的应用。凭借所使用的大量0.33数值孔径(NA)工具,EUV已证明其在技术上的强大,但是其可用性仍然是将EUV投入批量生产的门槛。在研发方面,EUV的研究现在大部分转移到了高数值孔径(NA≥0.5)的EUV技术。此次演讲中,介绍了EUV光刻概述其发展现状并详细描述该技术发展中所面临的主要挑战。最后,重点介绍了针对这些新兴挑战的所采取的的新研究设施和行动。

来自TechInsights的Jeongdong Choe介绍了所有主要的NAND制造商都在争相增加垂直3D NAND的数量,他们都推出了自己的9XL 3D NAND器件。与上一代3D NAND 64L和72L相比,产生了很多变化。此外,3D设计之间也存在差异。三星采用其独特的单垂直通道孔(VCH)蚀刻技术,并通过其92L V-NAND技术推出了256 Gb芯片和512 Gb芯片。东芝/ WDC将NAND串架构从单堆栈(64L)更改为双堆栈(48L + 48L),并且还采用了两步金属接触(MC)蚀刻工艺。目前,堆叠的垂直门总数已超过一百个,在智能手机上的使用也发生了从只使用2DNAND,到2D和3D NAND的结合,最后到现在如三星galaxy和苹果iPhone只具有3D NAND的转变,报告讨论了当前和未来的3D NAND架构,流程和设计,包括技术创新和存在的问题。

来自ASML Netherlands BV的Jo Finders报告指出,随着第五代NXE:3400的推出,ASML将EUV光刻技术引入了7纳米逻辑节点的大批量生产中。从最新的NXE:3400系统获得的光刻性能结果,数值孔径(NA)为0.33,光瞳填充率(PFR)为0.2,吞吐能力大于每小时125个晶圆。光刻胶工艺的进步将在未来推动更小的临界尺寸和更低的k1系数,先进的EUV标线可以增强对比度以实现低k1成像。另外,EUV使用的最佳掩模板类型取决于应用范畴。我们在衍射水平上对这些掩模进行了广泛的研究,分析了其在EUV中的适用性。

来自Tokyo Electron Limited的Hiromitsu Maejima(右下)报告显示在过去的十年中,多重投影技术被引入以协助光刻实现半导体器件的不断缩小。如今,EUV作为下一代光刻技术引入,成为继续保持器件缩减的候选技术。与此同时,针对最近的高生产率机器,工艺稳定性和机器质量是提高投资回报率的重点领域。匀胶机/显影系统(Coater/Developer System)的几个关键挑战是改善CDU控制,改善图案塌陷裕度以及EUV高产量解决方案中的缺陷减少。为了应对这些挑战,需要通过分析蚀刻后性能预算来持续改进硬件和工艺。另一个主要挑战是改善机器状态管理。为了应对这一挑战,需要增强晶片状态监控和日志数据分析。在本演讲中,作者将阐述最新的匀胶/显影工艺技术以及匀胶/ 显影系统的最新开发方向。

来自Canon的Keita Sakai的报告指出纳米压印光刻(Nanoimprintlithography, NIL)制造设备使用了一种图形化技术,通过喷射技术在基板上沉积低黏度抗蚀剂并将其曝光。首先图形掩模被放入到液态的光刻胶中,由于毛细作用液体会迅速填充到掩模中的缝隙。液体填充后,光刻胶在紫外线辐射下交联固化,然后去除掩模,从而在基板上留下图形化后的光刻胶。与投影光刻设备相比,该技术能够忠实地再现更高分辨率和均匀性的图形。此外,由于该技术不需要大口径透镜阵列和昂贵光源,因此纳米压印设备实现了更简单,更紧凑的设计,可将多个单元组合在一起以提高生产率。本工作改进了纳米压印设备中的对准系统以及高阶畸变校正(High Order Distortion Correction, HODC)系统,使测试晶圆和器件晶圆都具有更好的抗畸变和对准效果。此外还讨论了图案的化属性和成本。纳米压印光刻技术的分辨率和线宽粗糙度不受传统投影光刻方法的限制。由于纳米压印光刻技术采用单步图案化方法,因此与ArF浸没式光刻法相比,工艺成本大大降低。总体而言,纳米压印光刻技术目前实现了28%的成本优势,但是随着掩模寿命的不断提高,其成本优势变得更加显著。

来自Mentor的Liang Cao报告中指出,随着步入7纳米以下技术节点,半导体制造领域面临着更多挑战。对于半导体代工厂而言,工艺成功取决于其控制设计制造工艺窗口(design-manufacturingprocess window)的能力。它们不仅具有最大化工艺窗口的能力,还可以对坏点进行防范、检测、评估和修复,并能够在最快的时间内完成以上任务。但是,对现有设计制造工具继续进行缓慢而逐步的改善已经不足以应对上述挑战。设计工程师和工艺工程师对集成电路制造软件的精度和速度提出了更高的要求。与之对应的改进正在以机器学习的形式出现。机器学习技术带来了超越传统计算方式的新机遇。软件开发方面的最新进展使机器学习技术更易于解决工程和科学领域的问题。计算光刻技术也从这一发展中受益。通过应用机器学习来提出更好的解决方案。我们可以加快流片后的流程,减少循环周期,并更快,更准确地找到光刻坏点。此演讲讨论了从IC设计到制造过程中从Caliber平台构建的机器学习功能和应用,包括正在解决的问题,他们采用的解决方案,以及行业如何应用这些流程并实现收益。

来自Brion的Chris Spence的报告指出iPhone处理器技术的最新历史表明,集成电路技术的发展趋势是更先进的工艺节点,更小的特征尺寸和不断增长的晶体管密度。在消费者看来,这似乎是不可避免的趋势,但这种观点掩盖了半导体制造商及其供应商的辛勤工作。这项不懈的技术开发中一个特别的关键点是创建长期的技术路线图,路线图列出了5-10年内的对工具和工艺的要求。其中可能最著名的版本是ITRS路线图。这些路线图的真正价值在于明确了满足这些目标所需的具有挑战性的性能规范,因为这将驱动各种极具创造性的解决方案,这些解决方案可能需要对工具或流程进行完全的重新设计。在本次演讲中,ChrisSpence以个人经验为例,讨论了OPC模型的准确性:它是图形化技术精度的主要贡献者之一。他提供一个路线图,说明了工艺建模和图形校正所需的极高精度,以及此路线图的详细细分如何推动跨学科的解决方案:工艺仿真,计量,掩模制作和机器学习等。

自Synopsys的Xiangyu Zhou绍了对于几乎所有器件类型(存储器,逻辑器件,CMOS图像传感器等)而言,注入层在制造先进技术节点时都面临着特殊的挑战,因为衬底的形貌效应会在常规的光刻图案化中引起明显的边缘放置错误。在本文提出的流程中,他们正在使用严格的工艺仿真来准确建模和表征与图形拓扑相关的工艺影响,并部署经过制造验证的掩模校正引擎以有效补偿晶圆上的图案位移。展示了如何通过TCAD器件仿真扩展流程,使仿真结果不仅可以用于优化晶圆图形,而且还可以优化器件电气性能,从而实现全面的器件工艺联合优化(device-technology-co-optimization,DTCO)的解决方案。

来自YMTC的Zhiyang Song的报告提出了一种基于图像的OPC建模方法。该方法直接处理CD-SEM图像,而不是从SEM工具中提取测量信息。这个方法主要包括3个阶段:基于OPC目标GDS的图像匹配与清洗、黄金测量与处理图像的CD匹配、提取轮廓的测量信息。这种方法有三个优点。首先,它将最大限度地减少在不同图形之间负面影响的计量。其次,可以用它代替经验建立图像审查标准,从而降低OPC数据清理和SEM图像审查的成本。第三,它比传统的测量方法能更容易地提取出更多的量表,充分地提取和利用扫描电镜图像的信息。本文将演示一些演示案例,并介绍和讨论进一步的用法。

来自HLMC的Bin Zhao的报告介绍了根据rayleigh方程,Resolution = k1/,38nm半周期达到浸没式ArF的极限。在这种极端条件下,光刻工艺的发展和大规模生产面临着诸多挑战,本文就这两个主要问题进行了探讨。第一部分,工艺发展:介绍了照明ID的选择、胶片叠层的形成、版图的优化、OCL标记的设计,并对一些分割结果进行了比较,采用PWQ方法对薄弱环节进行了检查,对工艺窗口进行了评价。第二部分,量产:工艺窗口验证和变化控制,讨论了两种工艺变化情况:晶圆局部离焦和OVL特殊映射。

来自Shanghai IC R&DCenter的WeiYuan为大家介绍了在1x节点及以下的孔层OPC解决方案中,一种准确和鲁棒的SRAF插入方法是必不可少的。CTM(Continuous TransmissionMask)技术是一种新的迭代生成地图的方法,可以提取和放置比传统SRAF制导地图(SGM)精度更高的SRAF。然而,迭代计算会导致更长的运行时间,使得CTM在全芯片OPC中不实用。介绍了一种利用深卷积神经网络、(DCNN)技术生成CTM相关地图的新方法,该方法在保证运行成本的前提下,用户可以从CTM技术的高精度中获益。将这种机器学习技术应用于全芯片OPC中,实现SRAF的精确定位。通过比较晶圆数据,可以得出结论:机器学习SRAF提供了与CTM SRAF几乎相同的PV波段分布以及相同的处理窗口。在运行时,机器学习SRAF的速度比CTM快8倍,仅比SGM慢30%,是一种实用的全芯片解决方案。

来自Photronics的Henry Kamberian做了精彩的报告。在过去的几年里,业界在推进EUVL技术方面取得了重大进展,使其完全应用于7nm节点生产。然而,第一代EUV掩模的基础材料和设备仍然面临着巨大的挑战,掩模blank、图形技术、缺陷检测和修复以及缺陷的可印刷性是高产器件制造关键路径中最重要的因素之一。从本质上讲,掩模集成变得至关重要,因为晶圆光刻的边缘很紧,图形的变化有些不可预测,因此需要在掩模和晶圆之间达到新的集成水平。为此,我们必须研究并充分描述掩模图形、图形保真度及其变化,以确定对晶圆曝光和加工窗口的影响。在本次演讲中,重点讨论掩模图案的特性和图案保真度,以应对5nm及以上节点的复杂掩模设计挑战。我们将使用强调二维模式特征的掩模特征化方法进行深入分析。

来自Zeiss的Rolf Seltmann介绍了一种能够预防整体工艺偏移(overall excursion)、提高芯片性能的掩模调优方法。对于先进的半导体制造商而言,光刻和总体图案形成过程中的工艺控制至关重要。芯片良率取决于多种工艺的参数,需要引入复杂的在线测量。在整体光刻概念中,测量是通过仿真数据和真实曝光过程中光刻机收集到的在线数据来完成的。此外,还可以添加离线数据。由于焦距、剂量等输入参数存在较大偏差,测量算法需要在模拟中找到最薄弱的工艺环节。报告所介绍的预防工艺偏移(excursionprevention)方法致力于尽可能缩小关键输入参数的分布。并将这一概念应用于掩模调优,校正掩模CD,并最终改善场内的CD均匀性(intra-field CDU)。

来自Gigaphoton的Tommy Oga介绍了下一代ArF光源 “GT65A”。ArF浸没式光刻是一项具有前景的光刻技术,能够满足严格的工艺控制要求,同时提供高效的产率。下一代光源的研发目标是能进一步提高芯片的产量、满足可制造性。报告介绍了最新的线宽压窄模块(linenarrowing module,LNM),该模块能够减少光学元件和机械部件在激光照射期间的热效应。此外,LNM中的新型光学设计使其的使用寿命从60 Bpls延长到110 Bpls。因此,GT65A能够最大程度地提高提高生产效率,为芯片制造商提供最佳的运营成本。

来自ASML的Will Conley介绍了一种通过选择来自ArF光源的波长来提升DoF值的“多焦成像”技术(multi-focal imaging, MFI)。MFI技术能够针对特定的DoF需求进行调整,以确定所需的波长分离量。该技术创建了两个焦面位置。通过可开启/关闭的波长“抖动(dithering)”方法,从而消除任何潜在的光刻机对准问题。使用固定光源和掩模进行初步仿真模拟,结果表明,DoF值随波长分离得到提升。在晶圆上的单次曝光数据也已证实了DoF的改进。

来自上海集成电路研发中心的Qiang Wu做了有关5nm逻辑节点的光刻工艺设计的报告。该团队基于严格耦合波算法、阿贝成像模型、和EUV随机效应模型,自主开发了空间像仿真工具,并利用该仿真工具对典型的金属光刻工艺参数进行了优化。该团队与IMEC进行合作,利用来自数种光刻胶的晶圆曝光数据对仿真模型进行了校准。仿真结果表明,若想获得接近100%的成像对比度(对应31.4%的EL),意味着需要将最小pitch放宽到41nm以上(0.33NA的常规成像极限)。此外,由于EUV的数值孔径相比DUV较小,像差将会引起更明显的图形误差,为了满足2.5nm的总套刻误差,需要将像差引起的偏移保持在0.7-1nm以下。报告还讨论了EUV光刻中的掩模阴影效果,以及掩模三维散射效应。

来自中国科学院微电子研究所的Lisong Dong的报告主要展示光刻是集成电路(IC)制造的关键工艺。光学光刻系统使用光作为写入介质,将IC布局图案从掩模转移到晶圆上。根据瑞利准则,由最小可分辨关键尺寸(CD)表示的光刻分辨率与光照波长成正比。近来,具有13.5nm波长的极紫外(EUV)光刻技术已经开发成功,它被视为是5nm及以后技术节点半导体器件制造的最有前途的技术。迄今为止,几家领先的IC制造商已宣布开始在大批量制造工艺中应用EUV光刻。在高级光刻技术节点中使用EUV光刻已成为主流趋势。中国科学院微电子研究所关于EUV光刻的许多优化工作,包括使用基于学习框架的光源优化(SO),使用Proteus Workbench进行的光源掩模协同优化以及掩模优化。EUV-SO根据光源图形的稀疏先验公式转化为l1-norm重构问题。评价函数基于严格的成像模型建立,以考虑EUV光刻中的特征效应。根据7nm节点的规则,多晶硅周期为42nm,最小金属周期为32nm。使用Proteus Workbench设计测试图形并完成SMO。最后讨论了以上工作的仿真结果。

来自于Hisilicon的 Yanxiang Liu演讲中,设计工艺协同优化(DTCO)是在新技术节点的生命周期内进行技术定义,良率突破和产品提升的最关键考虑因素之一。与14nm节点中的7.5-track(7.5T)标准单元相比,12nm技术节点提供了一种低轨(low track)单元,可将面积减少多达20%。报告讨论了在固定单元高度下,紧密周期单向金属与相邻双向金属之间的工艺窗口的再平衡。此外,借助在单元、块以及全芯片水平上的光刻仿真预先定义了与图案相关的坏点,并利用选择性光学邻近校正(OPC)优化来改善坏点的工艺窗口。最后,作为DTCO应用的示例,总结了标准单元版图设计和优化、坏点检测和验证以及局部OPC提升和DFT实施的方法。

来自上海华力集成电路股份有限公司的Wenzhan Zhou介绍了随着IC制造进入20nm以下的技术节点,DFM变得越来越重要,以确保更高,更稳定的良率和更低的成本。但是,随着成熟的技术节点(例如14nm/ 12nm)引入新设计的硬件(1980i等)和控制算法(Focus APC),开始和Tier-1晶圆企业竞争的后来的晶圆场(Tier-2/3companies)期望得到更高的工艺窗口和更小的工艺变化。随着设备的提升,后来的公司可以再一次审视其DFM策略,以便弄清是否可以与设计人员共享改进的硬件/工艺/控制算法的好处。在报告中,使用了来自不同EDA供应商的OPC仿真工具,以查看通过光源掩码优化(SMO)将硬件/工艺/控制算法改进的好处转移到更为宽松的设计限制的可行性:1)更好的硬件:光刻机(更好的聚焦/曝光变化),CMP(intrafield topo),掩模CD变化(宽松的MEEF规格)等。2)新的工艺:从正向开发到负向开发。3)更好的控制方案:整体焦点反馈,反馈/前向对准控制,高阶CD均匀性改善;硬件和工艺中的所有这些收益都可以转移到更宽松的设计中,例如子设计规则结构工艺窗口(1D)和更小的E2E间隙(2D弱点)。

来自Mentor的Liang Cao指出设计优化在很大程度上依赖于工艺模型,这些工艺模型在物理上是严格的、经验上灵活且简单的。根据奥卡姆剃刀定律(Occam’srazor),如果可能的话,基于物理模型的工艺是首选。但是,随着先进的IC设计和制造复杂性的急剧增加,简单的设计规则更加不现实。相反,机器学习是一个真正的经验模型,具有很高的准确性。演讲描述了已被应用到多个应用领域的使用监督和无监督机器学习的机器学习平台。这些应用包括坏点预测、机器学习OPC加速、重定目标、蚀刻建模以及设计/版图分析。

来自Synopsys的Liang Zhu进行了关于SRAF的演讲。亚分辨率辅助图形已在光刻中得到广泛认可。一般来说,在主要设计图形周围的光学临近空间插入辅助图形,会改变相应主要图形的空间像强度剖面。优化辅助图形的放置可使主要图形获得最佳或更好的图像对比度,更好的成像分辨率和聚焦深度(DOF)。但是,最近的EUV光刻技术开发对边缘放置错误和工艺窗口控制提出了严格的要求,从而导致辅助图形变得越来越复杂。在这一领域,一维的辅助图形已不能满足如此严格的要求,而二维辅助图形在半导体行业已成为必需。本文回顾了对不同2D辅助图形类型的工艺窗口和边缘放置错误的评价以及它们相关的运行时间和内存消耗。评价了各种类型的二维辅助图形,包括45度断开辅助图形,45度连通辅助图形,仅曼哈顿(Manhattan only)辅助图形阵列等。生成辅助图形首先需要使用光学模型作为参考,生成基于模型的辅助图形规则表。然后,通过考虑辅助功能的尺寸和类型,将规则表分为不同的规则集。最后,将跨过程窗口的CD变化和边缘放置错误评估为每个辅助功能规则集的成功标准。此外,提出了一种基于反演光刻技术(ILT)的方法来生成优化的规则表,因为ILT在低k1光刻条件下,在寻找最佳的图形解以改善加工窗口、二维cd控制和分辨率方面具有相当大的优势。在本文的最后,总结讨论了如何使用诸如机器学习之类的前沿技术进一步优化辅助图形的放置。

来自上海集成电路研发中心的Yushu Yang报告了5nm EUV逻辑工艺流程的内容。5nm逻辑工艺是目前世界领先的晶圆厂正在开发或风险生产的前沿技术。在典型的5nm逻辑过程中,鳍片间距为22~27nm,接触多晶间距(CPP)为48~55nm,最小金属间距(MPP)为30~36nm。由于这些间距远小于193nm浸没式光刻的分辨率,这也是第一代大规模采用EUV光刻技术的光刻工艺,可以通过10层以上的单次曝光方法简化工艺流程。持续不断的推进给工艺集成带来了巨大的挑战,并将每个过程模块推向物理和材料极限。因此,流程开发的成功在很大程度上取决于仔细权衡利弊,以实现性能和产量目标。本文讨论了5nm逻辑工艺流程中关键工艺回路的不同工艺方法的优缺点,包括鳍片和金属栅回路中的先切后切法、自对准接触(SAC)与强对准接触(BAC)法、自对准双图形法。低金属工艺。基于以上评估,报告指出主要的流程挑战,并根据流程需求,为模块的流程开发提供建议。最后,考虑到刻蚀是半导体工艺中最重要的工艺模块之一,报告提出采用切割-最后方法的翅片环刻蚀模块技术规范(MTS),包括关键尺寸(CD)目标、CD均匀性、线宽粗糙度(LWR)和横截面轮廓要求。

来自上海集成电路研发中心的Yu Ding介绍了应用于5nm逻辑工艺流程的器件设计。集成电路制造商正在以各种形式采用FinFET技术,他们需要增加集成电路的密度,而避免使用过小的特征尺寸,以致器件性能下降。因此,FinFET晶体管技术使集成电路技术的发展继续遵循摩尔定律。FinFET(鳍式场效应晶体管)是一种类型的非平面晶体管,或称“三维”晶体管,可以是一个多栅器件,在一个基板上建造一个最大型的结构,在该基板上,栅位于两个、三个或四个侧面的沟道或在沟道周围,形成一个双栅结构。除了FinFET器件,纳米片器件也很受欢迎。由于FinFET工艺相对成熟,器件物理知识丰富,在5nm技术节点上仍然很受欢迎。目前,大多数5nmFinFET工艺技术都应用于移动和高性能计算应用。本文提出了一种基于5nm逻辑设计规则的高性能FinFET结构,该结构在工艺开发和维护方面面临着诸多挑战。为了实现对7nm器件15%的速度增益或25%的功耗降低这一具有挑战性的器件性能目标,报告研究了工艺性能和可变性。在前端工艺集成方案中,EUV光刻和高级蚀刻工艺将用于鳍形成、栅极图案化和沟槽接触形成。报告展示了模拟设备性能,如阈值电压、饱和漏电流、亚阈值斜率、漏引入势垒降低…这是基于首选的设备架构,并将通过从模拟结果中进行过程敏感性检查,提供关键维度和推荐主要性能优化方向。并简要介绍了电阻和电容的提取方法,以期对器件有一个很好的认识。

来自KLA的Kevin Huang展望了未来图形转移工艺面临的挑战:随着半导体器件在本质上变得越来越三维,图形控制不再局限于x-y平面。倾斜、剖面、形貌、晶圆形状、薄膜厚度等参数在z方向的变化成为影响器件性能和成品率的关键限制因素。光刻、沉积和蚀刻工艺之间日益紧密的集成是先进3D图案化的关键因素,需要模块内和模块间的优化。一个开放的架构、集中的工厂级数据仓库和分析平台,集成了所有工艺步骤的计量、检验和工艺数据,对于从源头快速识别和控制图形变化至关重要。报告介绍一些由KLA提供的范例,强调测量,分析和控制解决方案,以应对3D模式时代的挑战。

来自Ancchor Semiconductor的Abhishek Vikram报告了更有效的图形缺陷检测和计量方式。先进半导体器件的制造涉及数百个工艺步骤,并非所有相关工艺都表现出理想的性能,但它们需在容忍误差范围内执行。由于后续工艺的相互作用,即使是轻微的边缘工艺也可能导致下面任何工艺步骤的失败。因此,如果在该工艺的早期出现任何图形缺陷,则后续步骤中进行的所有工作都可能导致操作时间和资源的浪费。在半导体制造中,任何一种先进的制造设施都会受到这种图形变化的影响。该报告提供了使用图形中心的良率管理器和图形监视器解决方案来建立更有效的图形缺陷检测和度量的方法,该方法使用了基于图形的全芯片版图分析,并使用大数据信息来监控整个晶圆工艺参数,其不需要任何其它数据收集,而是使用现有的度量和检测数据来检测和监视图形变化。

来自长江存储的Andrew Zhang报告了3D NAND闪存技术研发和制造中的计量挑战·。3D NAND技术的研发和制造面临着缩小的器件的许多挑战,而计量技术在每一轮中都面临着更大的困难。与平面NAND不同,3D NAND具有高纵横比的三维垂直结构。显然,自上而下的图像不足以进行工艺控制,相反,内部结构控制变得比以前重要得多,例如,通道孔轮廓。此外,多层,特殊材料和YMTC独特的X-Tacking技术还带来了其它计量挑战:高晶圆弯曲度,应力感应套刻误差,不透明薄膜测量。技术研发可以采用某些破坏性方法,而制造只能使用非破坏性的方法。这些推动了一些新的计量学发展,包括X射线,质谱和中红外光谱。随着3D NAND供应商转向150层以上的设备,现有的计量工具将被推向极限,因此,计量必须创新。

来自长江存储的Xiaoye Ding报告了高性能3D NAND 通孔碟形测量的白光干涉解决方案。在传统的3D NAND设计中,外围电路约占芯片面积的20-30%,这降低了闪存的存储密度。随着3DNAND技术堆叠到128层或更高的层数,外围电路可能占芯片总面积的50%以上。相比之下,XtackingTM技术将阵列和逻辑部件布置在两个不同的晶圆上,并通过键合工艺将存储阵列连接到逻辑电路,以实现前所未有的高存储密度和高I / O速度。因此,通过深度监控以确保阵列逻辑连接的可靠性变得越来越重要。目前,AFM(原子力显微镜)是通孔深度监控的主要方法。AFM具有较高的精度,然而,低产能限制了其在批量生产中的使用,特别是当要填充的通孔金属被自然氧化时。为了满足批量生产的需求,研发了一种WLI(白光干涉)计量方法来监控通孔深度。WLI技术有两个主要的限制,透明薄膜的影响和衍射极限。该工作中,说明了具有超高精度碟形测量的工程解决方案。

来自JSR的Takanori Kawakami分享了面向5nm及以上节点的先进光刻材料现状。先进的器件制造需要高性能的光刻胶,如使用小的图形将图形从光刻胶转移到衬底上实现图形的转移。光刻技术正在将极紫外(EUV)运用到设备制造的过程中。EUV光刻技术目前处于第一代大批量生产阶段。单次曝光时,其所需的图形尺寸不超过20nm半周期,这就是为什么图形转移是另一个难题。下一代EUV光刻需要进一步提高光刻胶性能,例如分辨率,灵敏度和图形粗糙度。因此,深入了解5nm及以上的光子和材料的随机效应是非常重要的。另外,有各种各样的旋涂底层可以蚀刻衬底。 因此,旋涂下层材料在未来的光刻胶相容性,反射率控制,平面化和蚀刻性能方面变得很重要。JSR研发了先进的光刻胶和旋涂材料。在报告中,JSR展示了材料研发状况和性能以及潜在的基本特性,设计概念等。

来自瑞士保罗谢尔研究所的Dimitrios Kazazis博士介绍了用于高分辨率图形技术和光刻胶测试的极紫外线干涉光刻。深紫外线(DUV)浸没式光刻技术是目前用于半导体大批量生产(HVM)的光刻技术,由于受到使用的相对较大波长的限制,已达到其分辨率极限。13.5nm波长的极紫外(EUV)光刻技术是在7 nm及小技术节点上用于大批量生产的下一代光刻技术。在PaulScherrer研究所(PSI)的瑞士光源(SLS),报告在运行EUV干涉光刻(EUV-IL)平台上,该平台已成为学术和工业研究的强大工具。EUV-IL已成为一种有前途的纳米光刻方法,将干涉光刻的简单性与EUV光的短波长优势相结合。因此,EUV-IL是用于以高分辨率和高产量进行周期性图形技术化的并行制造工艺。与其他纳米图案技术相比,EUV-IL具有其他优势,例如,没有邻近效应,由于曝光时间短而对漂移不敏感以及对衬底充电不敏感,从而可以使用任何类型的衬底材料。因此,PSI的EUV-IL平台是光刻领域的世界领先工具,分辨率低至6nm半间距。该装置已用于多种应用中,例如等离激元结构(plasmonic structures),聚合物接枝(polymer grafting),纳米催化(nanocatalysis)和模板化组装(templated assembly)。

来自PiBond Oy的Vincent Chen介绍了用于先进和新型半导体制造工艺的硅基材料。化学放大有机光刻胶(CAR)已经在该行业使用了很多年。随着行业步入最后的鳍式场效应晶体管(FinFET)工艺节点,由于分辨率和线粗糙度的限制,在未来的极紫外线光刻(EUVL)图形技术中,可能更换这些材料。因此,无机材料已被认为是EUVL中有机CAR的可行替代品,并且近年来受到越来越多的关注。对用于高分辨率EUVL图案化的新型材料解决方案的需求,已导致可感知光刻堆叠的方式发生了重大变化。基于对新材料和新工艺的需求,PiBond研发了新型的硅基EUVL光刻胶,并将材料技术扩展到其他光刻波长,因为使用无机光刻胶材料可提供提高产量和整体工艺。图1已经证明了合理剂量的高分辨率图案。近期将讨论和总结基于硅的光刻胶材料以及光刻堆叠研发领域的最新成就。

来自江苏汉拓公司的Huayong Hu报告了光刻胶产品的研发。先进的光刻胶产品对于IC制造至关重要。在本次演讲中,报告介绍了研发团队的最新进展。第一个示例是覆盖12至16μm的超厚KrF(248nm)光刻胶,这对于制造3D NAND存储设备至关重要。在保持良好的耐蚀刻性的同时,成功解决了几个关键问题,例如高紫外线吸收率,较差的附着力和膜破裂。在ArF领域,已成功展示了在实验室中达到180nm间距(线/间距和接触孔)的能力。报告还提供一系列电子束光刻胶产品,从传统的正性PMMA到含负性Si的电子束光刻胶,分辨率高达10-15 nm。报告介绍的化学放大型电子束光刻胶(正负)均具有50nm或更小的分辨率。除了用于IC前端应用的光刻胶,还研发了覆盖20-110 um厚度的晶圆级封装负性光刻胶。总之,已经研发出25种用于IC和封装应用的光刻胶产品,旨在成长为中国IC行业主要的自主研发光刻胶供应商。

来自中科院长春应用化学研究所的Shengxiang Ji介绍了化学图案上的10纳米以下图形技术的高X嵌段共聚物定向自组装。嵌段共聚物(BCPs)在化学版图上的直接自组装(DSA)具有嵌段共聚物自组装和常规光刻的优点。BCP材料的DSA可以在大面积上形成周期性,完美配准(registered)和有序的纳米结构。聚(苯乙烯-甲基丙烯酸甲酯-b-甲基丙烯酸甲酯)(PS-b-PMMA)可能是研究最深入的BCP材料,因为PS和PMMA嵌段具有几乎相同的表面能(g),并且在热退火条件下在自由表面上表现出非优先润湿性条件。这种特殊的性能允许在热处理下在基板上形成垂直取向的畴,这对于BCP光刻至关重要。然而,PS-b-PMMA固有的相对较小的Flory-Huggins相互作用参数(χ)将最小的可访问域周期(L0)限制为~22 nm,而通常要求低于10 nm的特征,即L0 < 20 nm用于下一代光刻。在本次演讲中,报告介绍了在三种高χBCPs的设计,合成和DSA方面的最新工作:PS-b-PLA,PS-b-PLGA和PS-b-PMA。这些BCPs具有比PS-b-PMMA高得多的χ,可实现的最小的L0,即L0 <15 nm。

中国科学院重庆绿色智能技术研究所所长王德强研究员作《氦离子显微镜制造2D/ 3D纳米孔对DNA测序的技术》,王所长介绍了一种可扩展的方法来制造高质量的石墨烯纳米孔,并使用氦离子显微镜(HIM)进行生物分子检测的理论。HIM铣削在精确控制图形尺寸和形状方面显示出巨大优势,并且可能允许以晶片规模潜在地生产纳米孔。与诸如透射电子显微镜之类的固态纳米孔制造技术相比,HIM速度更快,在数分钟内就可完成从直径5到30 nm的不同尺寸纳米孔的制作。此外,王所长还介绍了石墨烯纳米孔形成的暴露时间依赖性:孔扩展的速率与暴露时间不是简单的线性关系,而是在短暴露时间下快速膨胀,而在长暴露时间下缓慢的现象。

复旦大学高分子系邓海教授作《先进光刻高分辨掩模材料的发展》的主题报告。邓海教授介绍了DSA高分辨率、低成本和退火时间短的特性,通过开发新的DSA光刻材料可以弥补国内光刻胶领域的短板。邓海教授还介绍了一系列用于DSA的含氟BCP,这些BCP的最佳半间距为5 nm或更小,表现出介于0.2到0.6的高c值,并且SAXS显示的分辨率高达4nm,在80℃下的热退火时间只有1分钟。

湖南大学的段辉高教授作《用于多尺度图案化的刻蚀和剥离(Sketchand Peel)光刻》的主题报告。段教授分享了一种独特的多尺度构图工艺,称为“Sketchand Peel”光刻。该工艺基于电子或离子束光刻,但与传统工艺相比,它在多尺度特征方面具有更高的图案通量和更高的分辨率。段教授还分享了将这种独特的过程在转移印刷以及柔性和可拉伸设备上的应用。

来自上海高等研究院的吴颜青研究员报告介绍了软X射线干涉光刻(XIL)具有高分辨率,清晰的空间像,高通量和大面积的特点。SSRF-XIL光束线的X射线具有良好的空间相干性,并且在实际条件下可以实现完整的空间相干性,X射线干涉光刻技术已被用于EUV光致抗蚀剂测试和纳米周期结构的制造。吴教授还介绍了SSRF-XIL站开发的新的XIL方法,例如高长宽比和大面积拼接XIL技术,宽带talbot效应并行直接写入等技术。

来自Paul Scherrer Institute的Xiaolong Wang 指出EUV光刻技术(EUV-IL)已成功用于光刻胶性能测试[1-3]. EUV-IL基于两个或多个13.5 nm波长的EUV衍射光束的干涉。一般使用两个周期为 Pg 的平行衍射光栅,两束一级衍射光在光刻胶涂层衬底表面发生干涉。尽管EUV-IL技术的理论分辨率极限为3.4 nm,但目前它受到高分辨率衍射光栅的限制,只能达到6 nm half-pitch(HP)的记录分辨率(record resolution),并提出了一种新的EUV-IL方案,其目标是将分辨率降低到8 nm。其设计的新型的衍射光栅用二阶衍射光代替一阶衍射光产生干涉图样,更易于制造。由于二阶衍射效率低,提出了一种新的方法来提高其衍射效率,使用原子层沉积(ALD),在 HSQ 光栅的顶部沉积一层氧化铪(HfO2)。

来自中国科学院化学研究所的Meng Su提出了一种3D液体自成型(self-shaping)方法,用于快速制备材料并精确实现微纳米尺度的结构。两个不同的量子点实现的3D架构有无干涉的光学特性,且特征分辨率低于3μm。三原色荧光纳米粒子也可以通过连续印刷结合在一起,并保持其各自的光致发光效率(5%差异)。黄色、红色、青色及白色均有清晰的交界面,以减少光学串扰效应。可以通过柱状硅模板诱导印刷组装纳米颗粒曲线,集成为柔性传感器,实现对人脸复杂表情的识别。不同的衬底上的某些节点之间会自发地形成最佳互连线,使电磁干扰降低65.9%。因此,在多功能光电子器件中,可以操纵液滴实现纳米材料的自组装。

以下是会议精彩瞬间: