第二届国际先进光刻技术研讨会胜利闭幕

▲参会嘉宾合影

2018年10月19日下午,第二届国际先进光刻技术研讨会胜利闭幕,本次会议为期两天,由集成电路产业技术创新战略联盟主办,中国科学院微电子研究所和厦门半导体投资集团有限公司承办,中国光学学会协办,中芯国际(SMIC)、长江存储(YMTC)、华虹集团、Mentor、ASML、Photronics、PDMCX、KLA Tencor、南大光电(Nata)、上海微电子装备(集团)股份有限公司(SMEE)、Toppan、JSR、Cymer、东方晶源、Synopsys、TEL、DOW、蔡司赞助。会议共有300余人参会,分别来自中国、美国、德国、日本等世界各地众多名企、厂商、科研机构、高校等。

会议开始,大会副主席,中国科学院微电子研究所所长、集成电路产业技术创新战略联盟副理事长兼秘书长叶甜春研究员,中国光学学会秘书长、浙江大学光电工程研究所所长刘旭教授,厦门市委常委、海沧区委书记、海沧台商投资区党工委书记林文生先后为大会致开幕词,大会秘书长、中科院微电子研究所计算光刻研发中心主任韦亚一研究员主持开幕式。按照大会安排,在这两天的时间里,来自Intel、IBM、ASML、Mentor等公司的特邀嘉宾分别就拟定的主题做了特邀报告,深入分析了光刻领域先进节点最新的技术手段和解决方案,内容丰富,包含7nm及以下先进节点的计算光刻技术、SMO、DTCO、EUV、DSA、Deep Learning、光刻设备、材料等。会后,参会嘉宾进行合影留念。

以下是会议详细内容:

▲会议开始,大会副主席,中国科学院微电子研究所所长、集成电路产业技术创新战略联盟副理事长兼秘书长叶甜春研究员致开幕词

▲中国光学学会秘书长、浙江大学光电工程研究所所长刘旭教授致开幕词

▲厦门市委常委、海沧区委书记、海沧台商投资区党工委书记林文生致开幕词

▲大会秘书长、中科院微电子研究所计算光刻研发中心主任韦亚一研究员主持开幕式

▲会议介绍

▲(1)来自来自Intel的Mark C.Phillips(左上)介绍,几十年来,对光刻设备的要求主要基于摩尔定律,通过减小波长和增大数值孔径(NA)来获得更高分辨率。这种相对简单的工作方式首先被多重图案化技术的发展所打破,目的是在EUV准备就绪前继续推进等比例缩小。多重图形化技术将最小器件特征尺寸从光学分辨率中分离出来,但是需要光刻工具的持续性升级以改善对套刻误差和关键尺寸的控制。随着光刻设备的套刻误差控制在10纳米以下,其他误差源开始成为边缘放置误差(Edge Placement Error,EPE)预算的重要部分。在未来的工艺节点,对曝光和量测工具的要求是能够提供符合节点设计规则的7-sigma 器件EPE分布。量测工具需要在工艺变化时保持准确性,并且能够在多重图形化技术的多个步骤中进行测量,以便获取和控制最终EPE的所有重要影响因素。

(2)来自IBM的Heike Riel(右上)首先介绍了在过去的50年中,芯片由“更小、更密集”的理念驱动着,不断实现着“更快、更廉价”的目标。实现同样功能的成本大大降低,同时系统的性能和可靠性有了显著的提升。然而目前单纯地缩小尺寸已经不再满足需求,必须采用多种途径来提升系统性能。为了进一步扩展核心逻辑器件与存储器件的技术革新,需要在材料、器件与架构上进行重大创新。

作者及其团队正在继续研展下一代的关键技术,例如,环栅纳米线与纳米片(gate-all-aroundnanowires and nanosheets)、用于高迁移率场效应管的III-V族化合物半导体纳米线(III-V semiconducting nanowires)以及用作陡坡器件(steep slope devices)的III-V族化合物异质结隧道场效应管(III-V heterostructuretunnel FETs)。与此同时,也存在着其它用于构建新系统、提升系统性能的技术,比如异构集成、3D封装、SoC、硅光子学(Silicon Photonics)等。

然而,尽管有着这些创新性的技术,增加晶体管密度的速度也已经放缓。这就出现了如何进行下一步发展的问题。在按比例缩放的传统芯片终结之后,信息技术的未来将会如何发展?在这方面,报告人认为应当发展全新的计算模式,例如量子计算和非冯诺依曼计算架构。后者会受到认知计算(Cognitive Computing)与物联网工作负载的极大影响。加速机器学习和深度学习是新计算系统所需的关键要求。

(3)来自ASML的Wim de Boeij(左下)报告显示浸没式光刻机仍然是半导体器件制造中关键的光刻设备。当逻辑器件节点小于5nm、DRAM器件节点小于18nm时,图形放置误差与层间套刻误差要求会越来越严格,因此,需要对浸没式光刻机系统进行改进。产品套刻误差要求控制在几个纳米,对光刻系统的再现性,准确性和稳定性提出了更为严格的要求。

该报告介绍了最新的浸没式和干式光刻机的性能,讨论了其中的一些系统和子系统/模块是如何改进光刻机套刻误差、聚焦和产量的。他们还提供了多个产品的套刻误差、成像、聚焦、产量和缺陷数据来进行证明。

他们特别关注新型的对准传感器。这种传感器性能有不少提高,以满足越来越苛刻的套刻误差要求。通过双极化检测和改进后的光学系统,其对准标记可检测性和对准精度方面取得了明显的进步。优化对准标记检测,可以减少标记不对称的影响,从而进一步提高标记精度。

(4)来自Mentor Graphics的Gandharv Bhatara(右下)报告显示在先进及新兴工艺节点中,系统性缺陷或者受设计风格影响的缺陷已经成为良率的限制因素。这些缺陷受制于半导体光刻工艺的发展水平。尽管光刻系统正在被推向极限,先进材料与光刻胶也被不断应用,但是临界工艺窗口(Marginal Process Window)仍然不足以支持半导体的密度缩放。显而易见的是,问题的解决方案不再仅仅依赖于OPC和RET技术的改进,而是仍然依赖于半导体供应链中的设计、工艺对操作输入及约束的管理。

在当下,问题依然存在,从设计集成、物理验证到半导体制造等方面,全都需要一些新颖的解决方案。

本次演讲重点介绍了目前最新的创新技术及解决方案,它们利用大量的进化算法和革命性计算技术,以满足以下行业需求:

1.减少验证循环,更快地完成设计并管理设计流程交互

2.创建和验证无坏点设计,确保平坦化(planarity)不会成为设计问题

3.通过使用高级OPC和RET了解工艺限制并扩展工艺余量

4.提高晶圆厂的生产力,缩短研发和生产周期,从而降低工艺复杂度及成本

▲(5)来自Brion的Yu Cao(左上)的报告指出随着半导体行业向7纳米及更先进节点发展,为了满足对精度和速度的不断增长的需求,计算光刻技术面临着新的挑战。要求其精度接近1nm,并且全球专用于OPC的运算量已经超过10 千万亿次每秒(PFLOPS),这一数值与世界上最强的超级计算机运算能力相当,需要消耗大量的成本。同时,相关技术领域的新发展机遇也令人兴奋:新的电子束测量系统提供了大量的数据;机器学习和新的计算架构进一步增强了用于建模和优化的新算法;新的图形化设备,例如EUV光刻机以及多光束光刻机(multi-beam mask writers)。本次演讲探讨了这些新的挑战,以及可能会引入计算光刻领域的新技术及其所带来的新发展趋势。

(6)来自Synopsys的Yongdong Wang(右上)报告中指出,随着半导体制造技术节点接近并超过7nm / 5nm,在DUV和EUV中为实现更高的分辨率,分辨率增强技术(RET)已经变得至关重要。在传统OPC中展现了优势的反演光刻技术(ILT)即是其中之一。利用S-Litho的ILT高精确度模型,实现了最优质的掩模版。妨碍ILT用于大规模生产的一大障碍是其运行时间。到目前为止,ILT主要针对代工厂用户的坏点修复以及存储器用户的单元级应用。通过Proteus ML平台,Yongdong Wang及其团队可以在保持掩模版相同优化程度的情况下,显著减少ILT运行时间。

(7)来自ICRD的Qiang Wu(左下)的报告介绍了自投影成像光刻工艺的早期发展以来,微光刻的能力经历了从零点几个微米到如今几十纳米的推进。在这段不算长的时间里,许多新技术都被快速应用到光刻领域中来,例如:准分子激光照明、化学放大光刻胶、抗反射涂层、高数值孔径透镜、包括OPC(光学邻近效应修正)和SMO(光源掩模协同优化)在内的各类分辨率增强技术、浸没式光刻技术、三层抗反射涂层、负显影技术等等。光刻工艺中的k1值从早期的0.5降低到如今接近0.25。许多工艺特征参数如聚焦深度(Depth of Focus)、线宽均匀性(Linewidth Uniformity)、套刻误差(Overlay)等,也都趋向更小的数值。但即便如此,仍有一些不变量存在。在本次报告中,伍强博士和大家分享他对光刻中的不变量的一些想法。报告将针对成像对比度、照明条件的选择、禁止周期、以及负显影等问题展开讨论。

(8)来自Photronics的Chris Progler(右下)介绍了在7nm逻辑器件以及1Z存储器节点,为ArF多重图形光刻提供掩模解决方案的需求已经促使他们实现了关键的掩模技术的进步,这些都集中在更高的掩模分辨率和更低的边缘放置误差(Edge Placement Error, EPE)上,同时他们提供了更高的掩模再现性和良率。由于该团队已经针对不同的逻辑和存储器应用调整了方案,掩模测量和检查方法直接在器件特性上强调了2D和3D图形的保真度。工艺仿真、数据建模和掩模工艺校正中的先进计算方法为制造的掩模提供了新的性能指标和输出可预测性,他们在1nm以下的掩模关键尺寸(Critical Dimension)的控制阈值实现突破。掩模集成方面,在复杂的多重图形光刻流程中,晶圆边缘和不可预测的图形可变性需要掩模和晶圆团队之间的联系更加紧密。对此,他们已经能够应对这些挑战,并开发了新的快速响应方法,以解决在高级逻辑和存储器中出现的坏点问题(Hotspot)。与此同时,EUV光刻技术也将要应用于大规模量产以降低多重图形化的复杂性。基于该团队5年前推出的EUV掩模开发计划,他们现在能够生产7nm节点的full field EUV掩模。当前技术已经不仅仅局限于接触层和阻挡层,也能够实现5nm节点金属层的单次曝光,这是推动当前EUV掩模发展的重要因素。EUV的工艺成本和生产周期都将取决于EUV掩模的良率和对EUV掩模图形化性能的预测。

本次演讲中Chris Progler探讨了解决ArF和EUV掩模挑战的进展、风险和机遇。同时还考虑了掩模技术在接下来的几个节点上的演变,因为半导体行业尝试利用EUV实现更高水平的掩模,并预测随着这种趋势掩模系统将会如何演变,这包括引入多光束直写和使用更高数值孔径的EUV。

▲(9)来自Toppan的Tom Obayashi(左上)的报告介绍了Toppan对下一代ArF浸没式以及EUV掩模的研究已经有所进展。先进的电子束直写技术已经成熟,并且光掩模生产工艺已经下降到10nm节点。目前,Toppan正在从材料方面研发新的技术,以确保达到7nm及以下节点的要求。本次会上,Tom Obayashi围绕光掩模技术的发展现状和面临的挑战展开报告。

(10)来自Carl Zeiss的Thomas Scherübl(右上)的报告介绍了自1993年推出以来,空间成像技术已成为光刻掩模制造的实际标准。蔡司的空间成像测量系统(AIMS™)通过光学测量系统来模拟扫描仪,该系统生成部分掩模的空间像,就像在扫描仪上看到晶圆的方式一样。这就允许我们用“扫描仪眼睛”观察和测量掩模。世界各地的掩模工厂维修验证和缺陷可图形化检查,在标准工艺中,由掩模检查工具检测到的缺陷首先由AIMS™检查它们是否会在晶片上成像,将会成像的缺陷修复并且在修复后对其进行评估以确保修复成功,若缺陷不再成像则意味着修复成功,检测采用的标准通常是相对于参考点或者峰值的CD差。因此,AIMS™允许在掩模场中进行光刻感知的掩模测量,而无需晶圆成像,这节省了掩模制造过程中的时间和成本。对于每一代的DUV扫描仪,蔡司一直向市场提供相应的AIMS™系统。EUV的引入引起了系统设计和开发模式的转变,因为EUV有其特定的要求和挑战,如反射镜、真空系统等。由于行业提出了对EUV HVM制造的AIMS™系统的需求,蔡司开发了AIMS™ EUV系统,并得到了Sematech和EMI联盟的支持。目前,第一批系统已经运往客户手中。本报告首先介绍了AIMS™技术及其主要应用,然后,针对系统设计中的主要挑战,特别是AIMS™ EUV系统,展示并讨论了有关修复验证等标准应用程序的结果和示例,最后,展示并讨论了新的EUV特定实例。一些出版物已经表明,EUV成像过程对掩模3D效应非常敏感,AIMS™技术则是测量掩模3D效应对最终空间成像的影响的完美方法。此外,在EUV中,随机效应变得更加重要,需要使用AIMS™ EUV平台上的特殊测量模式,该系统能够模拟空间图像中的随机性贡献,并且还可能模拟出潜在的晶圆成像。

(11)来自JSR的Toru KIMURA(左下)为大家介绍了先进节点的器件制造需要高性能的光刻胶及其相关材料,光刻胶图形质量必须非常高。对于ArF浸没式工艺来说,它的边缘粗糙度(LWR)需要小于2nm。光刻技术正在将极紫外线(EUV)引入集成电路制造中。在单次曝光时,光刻图形尺寸需达到小于20nm的半周期。用于先进节点的器件衬底是多种多样的。同时,具有3D结构的同种衬底也是种类各异。因此,考虑到光刻胶的兼容性、反射率的控制、平坦化和蚀刻特性等因素,其旋涂在层下材料的作用变得重要。在本次报告中,JSR介绍了其研发的先进的光刻胶和旋涂材料。JSR展示了其材料的性能、基础属性和设计概念等,它将支持JSR产品用于器件制造。

(12)来自DowDuPont的Zhijian (George) Lu(右下)做了精彩的报告。50多年来,光刻技术的创新对半导体行业的发展至关重要。如今,先进的光刻胶和图形增强材料正在以超越波长技术的速度实现小型化。Dow是全球最大的电子材料供应商之一,提供广泛的材料以供整个器件制造工艺使用,包括光刻,蚀刻,化学机械平坦化(Chemical mechanical planarization, CMP),清洗和先进封装。会上,吕博士讨论了新型光刻胶的产品和图形增强材料为现有的工艺带来质量、产量和缺陷的改善。

▲(13)来自Applied Materials的Chi-I Lang(左上)报道了存储器和逻辑器件的尺寸不断的缩小带来了诸多挑战,单靠先进的光刻技术无法解决这些挑战。即使业内能够克服光刻分辨率限制和EUV的随机效应,但器件良率仍要受边缘放置误差(EPE)的限制。因为在光刻、沉积和蚀刻过程中复合的不均匀性,造成了层状特征图形之间的未对准。通过SAxP和Lex等多重图形技术可以实现极小的周期线条,但是仍然存在许多挑战,如降低边缘粗糙度LER / LWR,周期波动,轮廓变化和图形负载。这些持续的挑战为材料解决方案提供了机会,进而促进了设备的发展。

本次演讲将探讨NAND,DRAM和逻辑器件的发展趋势,讨论影响EPE的工艺参数,并演示材料工程的作用,从而允许器件进一步缩放,并独立于图形化方案。

为了提高器件密度,NAND已经从2D转换为3D类型的缩放。沉积对的数量决定了器件的缩放,而不是分辨率。随着节点的推进,沉积对和层的数量将继续增加。增加的堆叠厚度要求先进的更薄的硬掩模材料和高选择性的蚀刻工艺,才能成功地蚀刻到通道孔的底部。对于DRAM和Logic,基于侧墙的图形化和自对准结构将是促进缩放的关键。最优选择PR衬底、轴心和侧墙材料,配合协同优化沉积和选择性蚀刻工艺开发,可以减少图形误差并减小EPE。蚀刻的选择性和方向性对于保持侧墙侧壁的保真度至关重要,同时确保在缝隙和核心区域完全去除侧墙。因此,侧墙材料应该集中在具有高选择性的材料上,同时在侧墙材料内应保持中性应力来实现保形性。除了基于侧墙的图形化之外,还可以使用新的工艺方案来创建自对准结构,来降低其对套刻误差和工艺变化的敏感性。这些方案包括ALD的沉积技术以及干法选择性蚀刻和CMP选择性去除技术。Chi-I Lang在会上讨论了几种材料系统并展示其对进一步实现缩放的结果,同时降低EPE并改善图形化性能的影响。

(14)来自Cymer的Will Conley(右上)指出对于所有的芯片制造商来说,都不愿意见到工艺中存在差异性。降低缺陷率是提高良率的关键,良率的提高意味着利润的提高。在DUV中,工艺窗口(Process Windows,PW)以及良率对光源提出了苛刻的要求。按照当前的技术,业界已经可以精确地识别到晶圆上的缺陷及其对工艺窗口的影响。ASML Brion的LMC(Lithography Manufacturing Checker)可以对坏点进行分析,Cymer的SmartPulse技术可以进一步评估线宽的敏感性。

Will Conley展示了最新的研究成果,提出了一种算法来描述光源带宽对热点的影响以及缺陷随线宽变化的规律。这种技术已经应用在了Cymer新机器的带宽控制上,并且已经证实了带宽的变化会引起缺陷水平的变化。利用已知的CD敏感性,通过测量激光带宽,就可以建立模型,来预测激光带宽对全局以及局部线宽均匀性的贡献。

(15)来自北京理工大学的李艳秋教授(左下)报告中指出,浸没式光刻正持续推进到10纳米及以下节点。与此同时,光刻质量对实际光刻系统的误差的敏感性提高了。换句话说,图形保真度和工艺稳定性与光刻机、掩模、工艺流程、测量等的误差和不确定性密切相关。为了补偿这样的误差,光刻机、掩模、工艺流程、以及测量的协同设计和优化应运而生。同时,低误差敏感性的分辨率增强技术(resolution enhancement technology with low error sensitivity, LES-RET)也发展起来。实验结果显示上述技术能够改善晶圆上的成像质量并显著增大光刻工艺窗口。

(16)来自University of Delaware的Gonzalo R. Arce(右下)介绍了随着集成电路的关键尺寸进入深亚波长领域,半导体工业越来越依赖计算光刻技术来进一步提高光刻系统的分辨率和图像保真度。光源优化是一种重要的计算光刻方法,其通过调制入射光线的方向和强度来补偿图像失真。由于快速增长的版图密度和像素化照明配置的引入,计算效率问题已经成为最先进的SO(Source Optimization)方法的一大挑战。本次演讲对自适应压缩感知(CS)算法进行了描述,且该算法可以提高传统CS方法的压缩效率。随后,将对基于自适应CS的光学光刻的快速SO方法进行介绍。另外,该报告还对采用不同算法的SO进行了比较和研究。

▲(17)来自KLA-Tencor的Satya Kurada(左上)的报告主要展示在过去的40年中,半导体制造中器件的关键尺寸从1000纳米发展到7纳米,与之伴随的,器件结构,材料,图案形成与制程技术,晶圆尺寸也都发生了转变。制程控制在这一系列转变中发挥了关键的导向性作用。制程控制中的检测,量测与数据分析等方法被广泛运用到整个半导体生态系统中,帮助识别制程问题并做出修正,推动IC制造商更快的完成高良率量产目标。作为最早引入晶圆制造厂的制程控制系统之一,在过往几代IC制造技术中,光学图案化晶圆检测系统是制造工艺流程中的关键部分。

今天的光学图案化晶圆缺陷检测系统,能够为业界各类器件结构,先进设计方案和制程技术提供关键缺陷的检测。为了达到相应的检测灵敏度,光学检测技术需要不断创新,包括开发功率强大的宽波段照射源,兼具波段可调功能,可变化的光学孔径;高速传感器与数据处理,将IC芯片设计特性与先进算法相结合。光学检测能力不断提升,能够捕获更小缺陷的同时,系统也在提高数据处理速度,以便为晶圆级检测提供快速的缺陷表征,同时也为产品批次特有的缺陷(前层的工艺问题)表征提供所需的产能。通过为先进技术提供速度和灵敏度,光学图案晶圆检测将继续为IC制造商提供必要的技术支持,包括在线监测,系统缺陷发现,制程窗口认证,光罩印制检查,制程调试以及对晶圆厂成功至关重要的其他许多应用。

(18)来自于Nova measuring instruments的 Barak Bringoltz(右上)在本次演讲中,他们对机器学习技术应用于光学关键尺寸(CD)测量的工艺流程进行了讨论,并展示了其取得的相关成果。同时,他们也集中展示了机器学习算法的组成,即这些算法能够自动地与大数据相结合,并且可以实现配方创建,配方监控与控制以及更新的自动化。这种自动化对半导体制造至关重要,因为工艺的稳定性难以实现,而且对半导体制造起着关键性的作用。另外,他们也讨论了利用机器学习与大数据系统相结合的算法来提高准确性和吞吐量。

(19)来自HLMC的Bi-Qiu (Dylan) Liu(左下)的报告指出,近年来套刻误差(Overlay)控制成为先进光刻工艺开发的关键挑战之一。在芯片尺寸缩小的驱动下,关键层的套刻误差设计变得越来越小。 28nm节点和14nm节点工艺的套刻误差要求分别为6nm和4.5nm,而10nm节点甚至需要低于3nm的套刻误差。对于成熟节点(例如,65nm,90nm)通常只需要维护好光刻机的性能,再应用线性补偿就能满足产品上(on-product)套刻误差的要求。但是,这种方法很难应用于于高级节点中。因此,行业亟需一种能够改进套刻误差的新方法,其应该包含以下几个方面:测量方法、测量标记设计、测量点采样(measurement site sampling)和补偿方法。所有这些领域都旨在实现同一个目标:套刻误差控制的准确性和稳定性。

与传统的基于图像的套刻误差(Image-basedoverlay, IBO)相比,基于衍射的套刻误差(Diffraction-based overlay, DBO)是一种更先进的测量方法。由于更复杂的算法、更稳定的信号检测和噪声滤波技术,DBO在精度和测量稳定性方面都超过了IBO。实验数据表明,与IBO相比,对于物理角度上相同的晶圆,DBO可以将套刻精度提高0.5-1nm。由于信号检测方法的改变,该技术需要重新设计DBO标记。此外还可以针对不同的工艺和掩模层进行定制化设计,以进一步提高测量精度和标记的可制造性。尽管这些额外的工作会增加设计的复杂度,但是考虑到准确度的提高,这样做仍然是值得的。

除了合格且更准确的测量标记外,测量采样是应该关注的另一领域。理想情况下,为补偿更严格的套刻误差要求,需要测量更多的点以采集必要的套刻指纹(overlay fingerprint)。但是,测量点数量会受测量速度的影响。因为测量速度比较慢,IBO测量点的数量是有限的,其结果与全图测量相比存在偏差。由于DBO在测量速度方面的优势,其在固定的时间内能够测量更多的点。此外,还可以应用智能采样方法,即使在稀疏采样时也能获得接近全图测量的指纹捕获性能。

最后,通过精确的标记设计和采用适当的采样方案,补偿系统最终决定了关键层的套刻对准结果。

线性参数控制不再满足于系统的需求,非线性参数控制已经成为基本的控制元素,此外其还可以减少反馈循环的次数。如何建立复杂且实时的反馈系统是先进光刻工艺研发的关键挑战。

HH的研究结果表明,通过改进测量方法和补偿方法,他们可以显着提高套刻精度和稳定性。这些方法将有效地用于先进光刻的工艺研发。

(20)来自Tokyo Electron Limited的Hiromitsu Maejima(右下)的报告说明半导体器件的不断缩小使得其制造成本大幅降低,半导体市场不断扩大。在过去十年中,引入了多图形化技术以协助光刻来实现连续缩放。预计EUV将作为下一代光刻技术并且成为下一个连续缩放的候选者。

同时,工艺稳定性(例如晶圆到晶圆和模块到模块的性能)和机器质量(例如Wafer-Per-Day稳定性和fast ramp-up的性能)是近年来高产率机器投资回报的重点领域。Coater / Developer系统面临的主要挑战有:提高边缘位置精度,关于多图形化的高产量解决方案的缺陷控制和EUV。为了应对这些挑战,需要对蚀刻后的性能预算进行分析,并对硬件和工艺进行持续改进。Coater / Developer系统的另一个关键挑战是改善机器状态管理。为了应对这一挑战,需要晶圆状态监测增强和日志数据分析。

在本次演讲中,其将概述最新的Coater /Developer工艺技术以及Coater / Developer系统未来十年的最新发展方向。

(21)来自Gigaphtoton的Sophia Hu(右上)的报告介绍了目前,业界使用的多重图形技术,仍是利用ArFi浸没式光刻实现的。这也对直接影响芯片的产能的ArFi浸没式光刻机提出了更高的要求。对光源来说最大的挑战,就是最大程度的提高ArFi光源的工作时长以最高限度的满足生产需求。

基于这个事实,SophiaHu指出通过引进新的技术可以延长模块的更换间隔以及降低机器的维护时间。这种技术不局限于光源,而是应该将设备维护周期、维护后工具的调整、工艺条件等都考虑在内。Sophia Hu展示了当前的结果,以及依据当前结果预测到的未来的发展方向。同时,Sophia Hu讨论了在机器使用效率最佳的情况下,如何进一步延长PM周期及其挑战。

(22)来自Canon的Keita Sakai(左上)的报告提到了纳米压印是一种有效的转移纳米尺度结构的技术。纳米压印设备所利用的技术是对一种低黏性的光刻胶进行逐场的淀积和曝光,其中的淀积是利用喷射技术(Jetting Technology)将光刻胶转移到衬底上,图形化的掩模压入光刻胶液体后,液体在毛细作用下迅速流入掩模空腔中,随后,光刻胶在紫外光的照射下产生交联,移去掩模,衬底上将留下图形化的光刻胶。与光学光刻相比,纳米压印能以更高的分辨率和更好的均匀性完成图形的转移。此外,先进光学光刻设备所要求的大直径透镜组和昂贵的光源,在纳米压印技术中均不做要求,因此纳米压印设备得以实现一种更简单、更紧凑的设计,将多单元整合一体,提高了产率。前人的研究已经证实纳米压印可以达到10nm以下的分辨率,使得这项技术适合于使用单一掩模的存储器的关键层。考虑到纳米压印系统中不存在复杂的光学器件,设备的成本得到降低,再加上简单的单级工艺和光刻胶的零浪费,这样的成本模型使纳米压印技术在半导体存储器制造领域的前景引人瞩目。

判断一项技术是否已准备好投入生产还取决于一些其他因素。对于压印光刻机,线宽均匀性(Critical Dimension Uniformity, CDU)和线边缘粗糙度(LineEdge Roughness, LER)都达到了2nm的标准,也实现了更小的套刻误差。另外,产率是一个对所有光刻工艺都有重要意义的参数,已有报道称,一台四工件台的纳米压印整机,可达到每小时90片晶圆的产率。

掩模方面,对CDU、图形放置精度(Image Placement Accuracy)和压印缺陷等都有严格的要求。半导体产业需要一种清晰的掩模设计理念,要求其不仅对主掩模和复制掩模都适用,也能兼容现有的6” x 6” x 0.25”标准掩模。

本次报告回顾了晶圆复制系统和掩模复制系统的研究进展。为了解决大规模制造的问题,将采用一种整合的方法,以满足产率和购置成本(Cost of Ownership, CoO)的要求。本次报告谈论了一种四工件台的纳米压印整机FPA-1200NZ2C的套刻误差、产率和缺陷方面的性能。为了提高套刻精度,安装了一种新的高阶失真校正(high order distortion correction, HODC)系统,并利用数字多镜设备(DigitalMulti-mirror Device, DMD),最终做到套刻误差小于3nm。纳米压印技术需要复制掩模,而其成功的关键在于粒子控制和图形放置精度。本次报告讨论了有关分辨率、图形放置精度和缺陷等问题的发展状况。

以下是分会场报告:

(23)来自复旦大学的Shisheng Xiong(左上)的报告讲解了基于微相分离的嵌段共聚物的定向自组装,是一种用于大规模生产与有效降低纳米加工成本的具有发展前景的研究。在过去的几十年中,半导体制造技术已经取得了巨大的进步,现在可以设计几十纳米尺寸的具有非均异质结材料的复杂系统(例如193i光刻)。然而,这些技术的进一步发展面临着极大的挑战,不仅是因为衍射极限,而且还因为设备成本过高。另一方面,自组装材料在分子尺度上自发地形成长程尺度的纳米结构,但是其材料在结构上完全自组装形成的微米区域或体积与工业相关设备以及设备系统下的宏观尺寸不相称。定向自组装(DSA)是自组装材料与传统制造工艺的集成。DSA是利用材料的自组装特性,同时满足制造的限制。从技术上讲,DSA在分辨率增强方面类似于双重图形技术。本次报告讨论了使用光刻定义的化学图形化表面来指导用于半导体制造的嵌段共聚物膜的自组装。

(24)来自Mentor的David Wang(右上)的报告讲解了众所周知,半导体存储器与它的设计以及与之相关的分辨率增强技术(RET)方案的制造工艺是分不开的。在先进节点和设计复杂性上,Design-to-Silicon提供了一个可图形化存储器特征的集成化分辨率增强技术解决方案和策略平台。工艺窗口(PW)、线宽均匀性(CDU)和容差质量的并行配置对于存储器图案化技术而言是极其关键的,尤其是对于存储器单元电路尺寸减小更是如此。通常关键层存储器版图需要反演光刻技术(ILT)和辅助ILT的分辨率增强技术(RET)解决方案,例如,基于光源 - 掩模协同优化(SMO)的pxOPC(一种光学临近效应修正技术)提供与CDU性能相关的高质量光源和掩模形状;在自动规则提取和重构之后,基于pxOPC的亚分辨率辅助图形(SRAF)对于全芯片存储器TO 特别有益,但对于任何类型的特征都需要寻找最佳的工艺窗口(PW)。设计与制造协同优化(DTCO)也常用于存储器生产中,其目的与使用RET工艺的目的相同。例如,在复杂的存储器TO情况下,基于进化算法的启发式优化可以实现ILT / RET技术方案难以解决的问题,此外,快速一致的OPC和SRAF放置是与存储器图案化技术相关的关键RET。软件允许快速处理分层和重复存储器特征以实现均匀输出,这不仅有利于掩模版TO,而且有利于实现晶圆上图形的一致性。最后,RET与整个存储器制造工艺的过程完整性控制交织在一起。每个工艺阶段可能需要不同的“存储器RET解决方案”。例如,对化学机械研磨(CMP)引起的工艺退化进行物理建模,并通过该模型引导的CMP智能填充到掩模对其修复;尽管晶圆坏点形式多变,但是可通过RET中的机械加工进行学习并预测。

(25)来自华中科技大学的Zongsong Gan(左下)的报告提到光刻作为芯片量产中最关键的技术,为了实现越来越小的特征尺寸以及越来越高的图形密度,其使用的波长一直在减小,从365nm到193nm,到现在的13.5nm,技术更新所需成本越来越高,摩尔定律是否可以延续也饱受质疑。

在不缩短波长的情况下,光学衍射极限是提高分辨率的最大限制。根据光的传播特性,是不能将光束聚焦到小于其波长一半的点的,这是1873年由德国科学家Ernst Karl Abbe首次观察到的现象。

为了突破这种光学衍射极限,ZongsongGan提出了一种利用两束不同颜色的光来提高光刻分辨率的方法。其中一束光通过聚焦透镜形成光斑,而另一束光则是环状的,而且和光环具有相同的圆心。同时,需要有一种特殊的光刻胶,这种光刻胶在这两种光照下具有相反的反应机理。外围的环状光束就可以削弱中心光斑的效果,从而实现更小的线宽。通过控制环状光束的强度,就可以控制线宽的大小。通过这种方法,已经可以实现9nm宽的线条,以及周期为52nm的线条。

这种方法的优势在使用可见光就可以实现更低分辨率,可以很大程度降低生产成本。

(26)来自Kempur Microelectronics的Mark Neisser(右下)的报告显示多年来,技术路线图已经成为半导体行业的一部分。最早出现的路线图是摩尔定律,起初它是一种对行业竞争的经验性观察,后来转变为一个预测,成为整个行业的路线图。之后又发展了ITRS路线图,多年来,行业领先的半导体制造商一直在采用它来推动所需的新技术。IRDS路线图预测半导体终端用户的需求,并根据这些需求制定技术路线图。2017 IRDS路线图刚刚发布。为了制定路线图,作者团队吸收了来自世界各地的专家的意见。该路线图对高性能逻辑要求的预测将推动逻辑芯片中不同器件结构的发展。随着存储技术的进步,人们关注的重点更多在于成本而非性能。因此,对于不同类型的设备,技术路线图也可能存在差异。例如逻辑器件将采用EUV及其扩展,而闪存将考虑纳米压印。定向自组装(Directed Self-Assembly, DSA)和直写电子束 (direct write e-beam)也正在研发中。DSA具有提高CD均匀性和降低成本的潜力;直写电子束则有望实现芯片的个性化。DRAM存储器将在关键尺寸上跟随逻辑器件,当EUV变得具有成本效益时,也将采用EUV,这要求EUV能够正常工作并克服关键尺寸与光刻胶随机性的挑战。而在存储器方面,或将尝试使纳米压印成为可靠且低缺陷的加工方式。从长远来看,逻辑器件有望在2020年末开始转向3D架构。这将给图形工艺的产量以及减少所需的流程步骤数带来巨大压力。同时还需要关注孔型图形,这也将会成为未来关键图形的挑战之一。

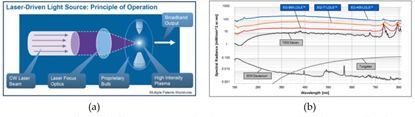

(27)来自Energetiq Technology的Huiling Zhu(左上)的报告介绍了在半导体制造中,对于先进工艺控制的光学测量工具来说,激光驱动光源(LDLS)是理想的辐射源,它具有超高亮度和宽波长范围。 LDLS光源具有190nm至2400nm的波长范围,这一优势使其已被广泛应用于光谱椭偏仪(SE),光谱散射仪(SS)和白光干涉测量(WLI)应用的批量制造中,用于测量关键尺寸(CD)、套刻和薄膜厚度。 LDLS光源与市场上其他光源不同,它们使用二极管激光器或光纤激光器在高压Xe灯泡的中心提供聚焦激光束,以激发高温小体积Xe等离子体。与传统的宽带光源相比,LDLS灯具有更高的亮度、更长的寿命、更好的稳定性和更宽的波长范围,适合许多半导体光学测量应用。由于其设计原理,LDLS等离子体不能通过穿过Xe灯泡电极的电流来维持,而是通过对聚焦激光光能的Xe等离子体吸收来维持。这种新颖的能量输送方法消除了电极材料在运行过程中的蒸发和溅射,因此Xe灯泡壁能够保持清洁,输出维护率显著提高。由于消除了传统短弧灯中等离子体和电极的相互作用,LDLS中的Xe等离子体还具有更高的空间稳定性和时间稳定性。由于强聚焦的激光束,LDLS等离子体以较高的功率密度被激发,因此等离子体核心温度远高于DC放电Xe等离子体,从而实现更高的亮度。LDLS工作原理和典型的光谱辐射性能数据如图1所示。

图1.激光驱动光源(LDLS),(a)工作原理; (b)与传统宽带光源的光谱辐射性能比较

自由空间输出LDLS源具有0.5NA输出窗口。折射或反射光学器件可用于收集0.5NA输出光并操纵光束以适应各种应用。报告将讨论用于光学测量应用的宽带光束操纵和传输的一些样本光学器件,还将介绍具有光纤耦合输出的LDLS源的参数。

(28)来自Hamamatsu Photonics的Chenghao Xiang(右上)的报告介绍了更小的关键尺寸(14nm或更低)和高集成度带来许多物理缺陷,致使代工厂面临着产量低和产品功能性失效的问题,从而导致半导体技术的发展很难跟上日益增长的消费市场。在这种情况下,量测和监控技术对于半导体工业的发展是空前重要的。这些技术通常可以分为光学解决方案和电子束解决方案两类。具有鲁棒性、高产量和高分辨率的光学计量和检测以及故障分析系统在量测和监控市场中占据很大的市场份额。此外,为了提高产量,在半导体工艺设备中通常采用光学传感器和光源作为监控终点和条件。Hamamatsu Photonics目前致力于工业市场的光学量测和监控系统中的发射器和接收器,服务于半导体设备制造商,代工厂和研究机构。文章主要讨论了波长范围从X射线、紫外到红外的光发射器和探测器及其应用,以及它们是如何提高半导体工艺产量和精度的。随后,展示了在图像传感器、光电倍增管/模块、硅光电倍增管/模块、雪崩光电二极管/阵列、微型光谱仪、空间光调制器等器件中选择最佳光学传感器的方法。作为发射器的光源应该与接收器有良好的匹配,还介绍了如何选择它们进行集成。此外,为了快速定位故障或缺陷,Hamamatsu Photonics强烈建议半导体设备制造商、设计人员、代工厂和研究机构使用具有时序分析、OBIRCH分析、热分析和发射分析功能的光电发射显微镜(photoemission microscopes)以及有望在故障分析中使用的红外摄像机。总之,HamamatsuPhotonics提供各种光源和光学传感器/探测器/模块以及故障分析系统,以帮助半导体参与者提高产量并获得更多利润。

(29)来自同济大学的Xing-Yu Zhou(左下)的报告提到了在先进的半导体光刻制造工艺中,亚波长光刻间隙(sub-wavelength lithography gap)可能产生光刻误差,进而导致晶圆图形和掩模图形之间的差异,他们可能在后续工艺中引起晶圆缺陷。即使版图通过了设计规则检查(Design Rule Check, DRC),其中仍然可能存在对光刻工艺敏感的坏点图形。因此,工艺坏点检测已成为行业的一个关键问题。本演讲介绍了一种基于卷积神经网络(CNN)的工艺坏点检测框架。比较了不同的网络参数对检测性能的影响,包括训练批量、学习率、损失函数和优化方法,并针对典型的基准(benchmark)给出了最优参数。这种改进模型的性能优于常见的机器学习方法。同时本框架给出了一种通用的训练流程。这种灵活的训练方法可以应用于不同的测试基准,以获得更好的坏点检测性能。

▲会议提问环节

▲会议现场

▲会间茶歇